本文旨在介紹Ansys Lumerical針對(duì)有源光子集成電路中PN耗盡型移相器的仿真分析方法�。通過FDE和CHARGE求解器模擬并計(jì)算移相器的性能指標(biāo)(如電容�、有效折射率擾動(dòng)和損耗等)�����,并創(chuàng)建用于INTERCONNECT的緊湊模型����,然后將其表征到INTERCONNECT的測(cè)試電路中實(shí)現(xiàn),模擬反向偏置電壓對(duì)電路中信號(hào)相移的影響���。

這里假設(shè)移相器的結(jié)構(gòu)沿光傳播方向是均勻的�,因此僅模擬器件的橫截面�����。我們將演示每個(gè)部分的仿真及結(jié)果��。

步驟1:電學(xué)模擬

利用CHARGE求解器對(duì)移相器組件進(jìn)行電學(xué)模擬�����,獲得電荷載流子的空間分布作為偏置電壓的函數(shù)����,并將電荷分布數(shù)據(jù)導(dǎo)出為charge.mat文件。根據(jù)載流子濃度����,我們也可以估計(jì)器件電容。

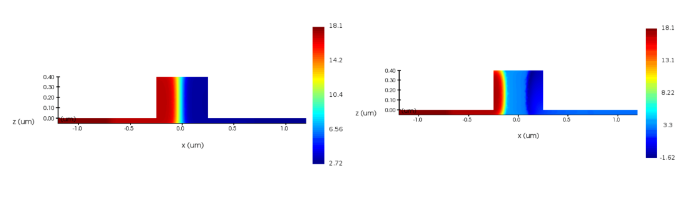

施加于器件的偏置電壓為0V(左)和-4V(右)時(shí)�����,移相器橫截面的電子分布曲線如下圖所示:

由圖可知���,在沒有施加偏置電壓情況下��,波導(dǎo)橫截面上的電荷分布是對(duì)稱的���。通過施加足夠強(qiáng)的反向偏壓,由于pn結(jié)上耗盡區(qū)的加寬���,電子被部分推出波導(dǎo)(向左)�,導(dǎo)致波導(dǎo)上電荷分布發(fā)生相當(dāng)顯著的變化����。

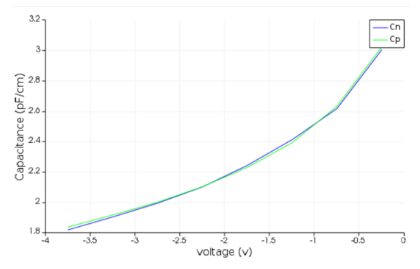

電荷分布和耗盡區(qū)寬度的變化將改變結(jié)電容,器件的C-V曲線如下圖所示:

由圖可知,電子和空穴對(duì)結(jié)電容的貢獻(xiàn)非常相似����,且由于耗盡區(qū)加寬,隨著施加更高的反向偏置電壓����,二者對(duì)結(jié)電容的貢獻(xiàn)降低。電容的大小會(huì)影響移相器的工作速度(帶寬)���,因此可以在電路模型中考慮這種影響��。

利用MODE求解器中的FDE模塊進(jìn)行光學(xué)模擬���,從電學(xué)模擬獲得的變化的載流子濃度改變了波導(dǎo)的折射率,所以波導(dǎo)的有效折射率與偏置電壓有關(guān)�����。將第 一步得到的電荷分布數(shù)據(jù)charge.mat加載到FDE求解器中���,這里需要兩個(gè)模擬來表征波導(dǎo)。

偏置電壓設(shè)置為0��,使用頻率掃描獲得波導(dǎo)在0偏壓的有效折射率關(guān)于頻率的函數(shù),波導(dǎo)數(shù)據(jù)導(dǎo)出為ps_active_0.ldf����。

使用Sweep進(jìn)行電壓參數(shù)掃描,計(jì)算中心波長(zhǎng)處的有效折射率和損耗隨偏置電壓的變化��,數(shù)據(jù)導(dǎo)出為neff_V.dat����。

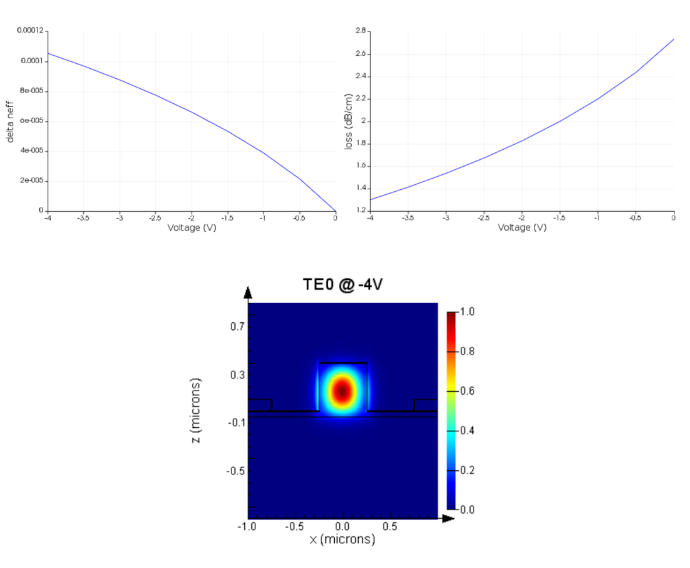

有效折射率、損耗和偏置電壓的關(guān)系曲線以及模場(chǎng)分布如下圖所示:

由圖可知����,較大的反向偏置引起較高的有效折射率擾動(dòng)和較低的損耗。這是因?yàn)槭┘恿朔聪蚱珘汉?,波?dǎo)內(nèi)自由載流子的耗盡會(huì)減少沿波導(dǎo)方向的光吸收量,較高的折射率擾動(dòng)可以減小移相器實(shí)現(xiàn)π相移所需的長(zhǎng)度��。在-4V偏壓下�,移相器在1550 nm下的TE模被很好地限制在波導(dǎo)內(nèi),與波導(dǎo)內(nèi)的載流子分布顯著重疊����,這可以顯著地影響模式的有效折射率。

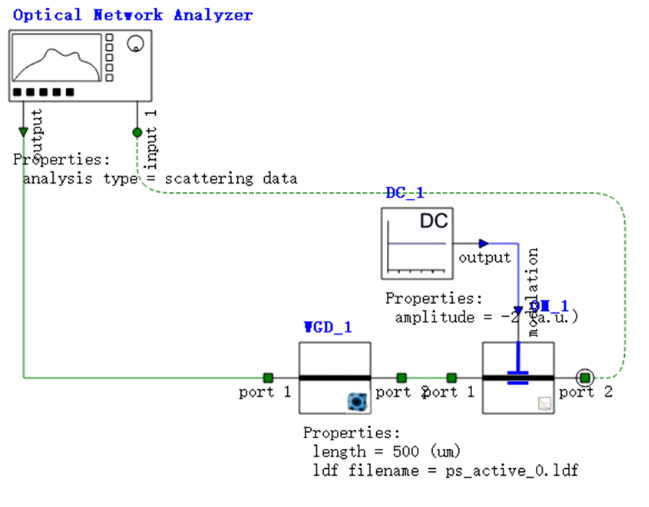

將步驟2中的仿真結(jié)果加載到INTERCONNECT電路中的相關(guān)元件中��,利用INTERCONNECT測(cè)試移相器元件在簡(jiǎn)單電路中的性能,使用光網(wǎng)絡(luò)分析儀計(jì)算器件的頻域響應(yīng)��。

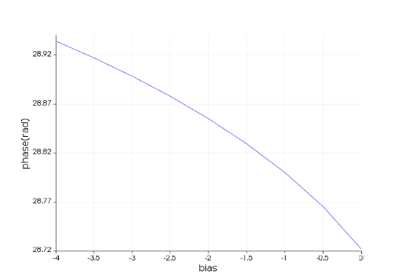

不同偏置電壓下的相移曲線如下圖所示:

由圖可知�,隨著偏置電壓的變化,相位發(fā)生了變化��。仿真結(jié)果表明��,對(duì)于 500 微米的長(zhǎng)度�����,在 4 伏偏置電壓下相移約為 0.2 弧度��,這表明移相器的 Vπ.Lπ 品質(zhì)因數(shù)約為 0.03 Vm����。

相關(guān)閱讀

使用 Lumerical 對(duì)鐵電波導(dǎo)調(diào)制器進(jìn)行仿真應(yīng)用

Lumerical 納米線柵偏振器仿真應(yīng)用

Lumerical EME 求解器的多核調(diào)用

Ansys Lumerical 關(guān)于 CMOS 傳感器的串?dāng)_和量子效率仿真方法

Lumerical 關(guān)于 CMOS Image Sensor 的寬帶模擬

Lumerical 針對(duì) CMOS image sensor 仿真中的角度響應(yīng)

Lumerical 單光子雪崩二極管仿真

基于 Lumerical 的雪崩光電二極管仿真

Lumerical針對(duì)MicroLED的仿真實(shí)例

Lumerical 針對(duì)多模干涉耦合器的仿真設(shè)計(jì)與優(yōu)化